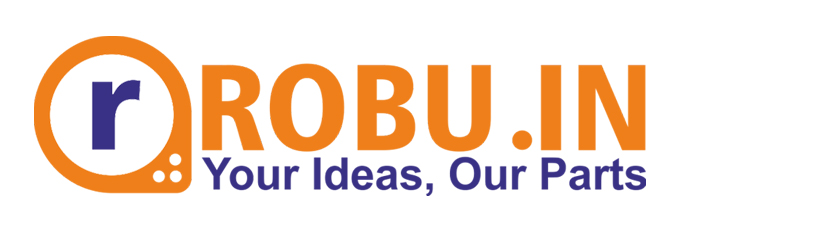

The IOP (Internet Offload Processor) WIZnet W7500P is the one-chip solution that integrates an ARM Cortex-M0, 128KB Flash, and hardwired TCP/IP core & PHY for various embedded application platforms especially requiring ‘Internet of things’.

The TCP/IP core is a market-proven hardwired TCP/IP stack with an integrated Ethernet MAC. The Hardwired TCP/IP stack supports the TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE which has been used in various applications for years. WIZnet W7500PP suits best users who need Internet connectivity for applications.

Note: For more technical details go through Datasheet in the attachment section

Features:

- 48MHz maximum frequency

- 8 Sockets

- SRAM for socket: Max. 32KB

- MII (Medium-Independent Interface)

- IC Plus (IP101G)

- Flash: 128 KB

- SRAM: 16KB to 48 KB ( Min 16KB available if 32KB socket buffer is used, Max 48KB available if no socket buffer is used)

- ROM for boot code: 6KB

- POR (Power-On Reset)

- Internal Voltage Regulator: 3.3V to 1.5V

- 8-to-24MHz external crystal oscillator

- Internal 8MHz RC Oscillator

- PLL for CPU clock

- 12bit, 8ch, 1Msps

- 6-channel DMA controller

- Peripheral supported: UARTs, SPIs

- 34 I/Os (15 IO x 2ea, 4 IO x 1ea)

- Serial Wire Debug (SWD)

- 1 Watchdog (32-bit down-counter)

- 4 Timers (32-bit or 16-bit down-counter)

- 8 PWMs (32-bit counter/timers with programmable 6-bit prescaler)

- 3 UART (2 UARTs with FIFO and Flow Control, 1 simple UART)

- 2 SPI

- 2 I2C (Master/Slave, Fast-mode (400 kbps))

- 1 RNG (Random Number Generator): 32-bit random number

Package Includes:

1 x WIZnet W7500P

There are no reviews yet.